When we are doing the scan insertion, we may find many uncontrollable clocks and uncontrollable asynchronous signals like set and reset violations. How to avoid these violations?

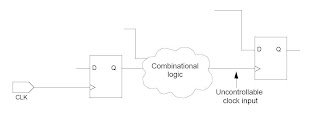

Uncontrollable clocks are coming from a combinational logic (Clock Dividers). When doing scan insertion, the control of the FF must be with respect to the TEST EN signal, ie, if TEST EN = 1, the whole chip should be in scan mode. For this all the clock of FF should be controllable at the top level.

Wherever you get a uncontrollable clock violations, please do the following :

Wherever you get a uncontrollable clock violations, please do the following :- MUX the functional CLK with the "test clk" with the TM(Test_Mode) as the select line and then give the output of MUX as the input to the FF.

You can also use Auto-Fix to fix uncontrollable clocks and asynchronous sets and resets.

Auto-Fix can automatically fix each uncontrollable clock input as shown in Figure.

To use the Auto-fix capability:

Use the set_dft_configuration command to enable the various Auto-fix options:

To fix the uncontrollable clock, use the option -fix_clock_enable

To fix the uncontrollable asynchronous set signals, use the option -fix_set_enable

To fix the uncontrollable asynchronous reset signals, use the option -fix_reset_enable

# Enable AutoFix

set_dft_configuration -fix_clock enable \

-fix_reset enable -fix_set enable

Auto-Fix can automatically fix each uncontrollable clock input as shown in Figure.

To use the Auto-fix capability:

Use the set_dft_configuration command to enable the various Auto-fix options:

To fix the uncontrollable clock, use the option -fix_clock_enable

To fix the uncontrollable asynchronous set signals, use the option -fix_set_enable

To fix the uncontrollable asynchronous reset signals, use the option -fix_reset_enable

# Enable AutoFix

set_dft_configuration -fix_clock enable \

-fix_reset enable -fix_set enable

No comments:

Post a Comment